HIGH-PERFORMANCE-SENSORSYSTEME durch Verbindung von Siliziumtechnologie und keramischer Mehrlagentechnik

Powered by SiCer - The best of both worlds

Silicon-ceramic composite substrates - from the laboratory to a robust process technology

Marc Bochard | VIA electronic GmbH

Cathleen Kleinholz | Technische Universität Ilmena

Thüringer Werkstofftag 2021

Silicon-ceramic composite substrates – from the laboratory to a robust process technology

MON THROUGHER

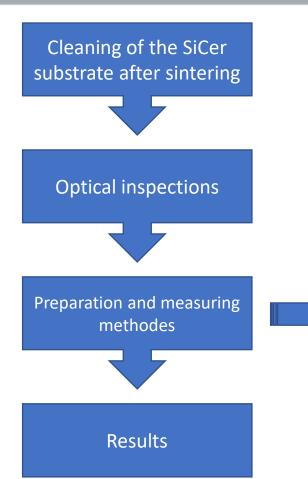

# Agenda

- 1. Introduction

- 2. Manufacturing process of SiCer-substrats

- 3. Fabrication of cavities

- 1. in ceramic

- 2. in silicon

- 4. Layout and process optimization

- 5. Analysis and measurement results

- 6. Conclusion and Outlook

## 1. Introduction

#### Advantages and special properties of SiCer sensor applications:

- high temperature stability

- manufacturing and 3D-integration at wafer-level

- high bond strength at the interface

#### **Challenges:**

- manufacturing and stability of cavities geometry

- (in one or both materials)

- defect-free bonding-interface

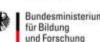

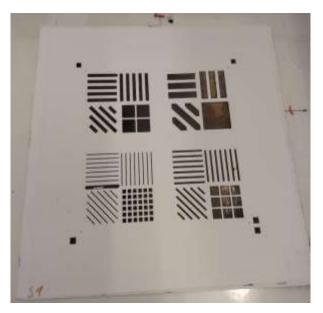

Ceramic membrane after sintering process

### → process optimization necessary

#### 1. Introduction

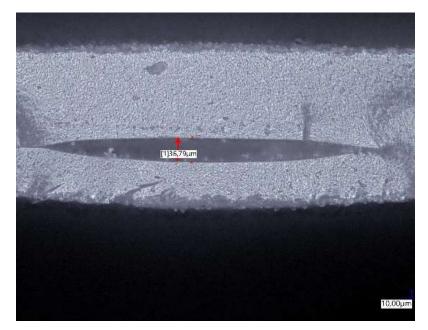

State of the art in SiCer technology and beyond

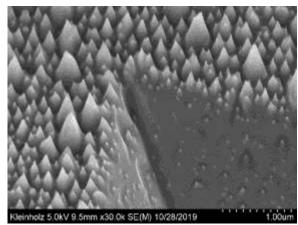

without the polymer binder. (b) Si that has been nanotextured by RIE. (c) The textured Si after treatment with argon plasma. (d) A view of the bond interface with nano structures after sintering.

Figure 3. A set of SEM images showing stages in the development of BCT. (a) A view of the powder morphology of BCT

#### BCT6

quartz as non melting filler / sodium-free glass component DINCH plasticizer (1.2-cyclohexane dicarboxylic acid diisononyl

ester)

To improve the bonding between Si and Cer, the wetting must be increased.

TiO2 as adhesion promoter (increasing hydrophilicity)

# TiO2 layer + nanostructuring enhance the bonding significantly by increasing the wettability

Thüringer Werkstofftag 2021

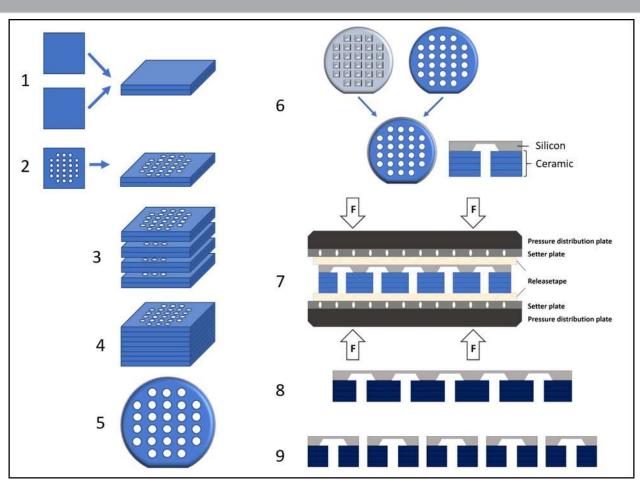

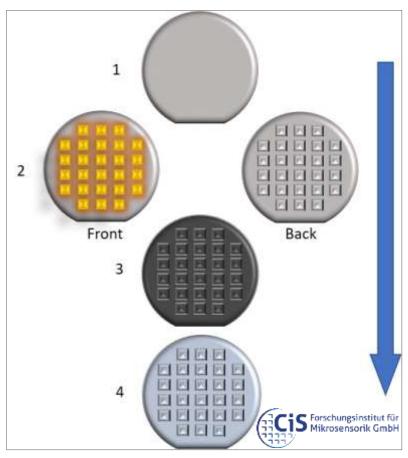

## 2. SiCer Manufacturing process

- 1. tape preparation

- 2. punching of cavities, screen printing, via filling

- 3. stacking of double tapes (for process stability)

- 4. isostatic lamination

- 5. laser cutting or punching of wafer contour

- 6. SiCer stacking

- 7. sinter process

- 8. post-processing

- 9. single chip module

Process sequence of SiCer-substrate production [3]

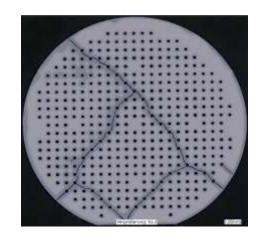

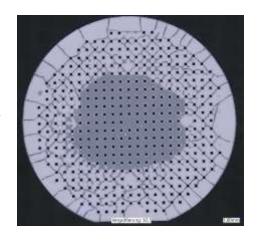

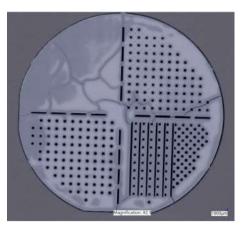

Towards defect-free SiCer composite with open cavities

Cracking, insufficient bonding

In parts better adhesion, more cracking on the outer side

In parts better adhesion, Significantly less cracking

Light grey: Insuffisant or inexistant bonding

Dark grey: Good bonding

No cracks, defect-free bond

Lamination process adaptation:

Higher pressure

Higher temperature

Longer process duration

Cavity structure modification to relax the mechanical stress during sintering Cavity structure modification to relax the mechanical stress during sintering – 1 single sheet

Thüringer Werkstofftag 2021

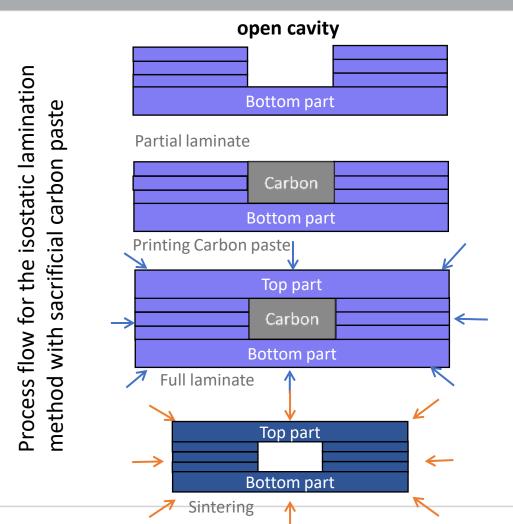

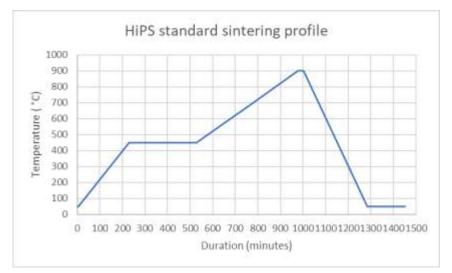

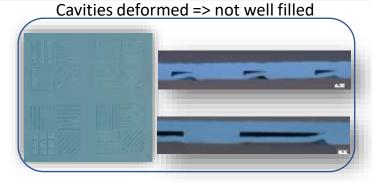

Sintering profile needs to be modifed to enable carbon burn out before the pore closure.

Thüringer Werkstofftag 2021

Silicon-ceramic composite substrates – from the laboratory to a robust process technology

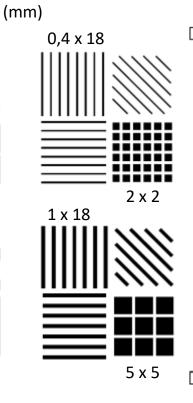

Filling deep cavities by **screen printing** of carbon paste\_green state

First print

#### **Solutions:**

- use stencil instead of screen

- Depending on the depth of the cavities, the printing process must be must be adjusted

Second print

Thüringer Werkstofftag 2021

Third print

6,372

Enhanced sintering profile 1000 900 800 Temperature (°C) 600 Carbon 500 burning 400 300 630°C, 1 hour 200 100 0 100 200 300 400 500 600 700 800 900 100011001200130014001500 Duration (minutes)

Filling the cavities Stencil printing

Full laminate

| Layer | Material | Thickness<br>green [µm] | Size    |

|-------|----------|-------------------------|---------|

| 1-5   | ВСТ6     | ca. 250                 | 115x115 |

L2 L3

Sintered (1h burning out phase at 630°C added)

Each layer is created with 2 BCT6 tapes

Shrinkage ratio in Z direction: ~50%

Thüringer Werkstofftag 2021

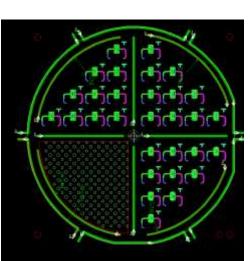

#### **Structural elements:**

Buried channels and cavities

tapes) bonded to Si

Crack formation at wafer level

DP951 PX and BCT6

**DP951**, Screen printed carbon paste

**SiCer** test structure with integrated fluidics

BCT6, Stencil printed carbon paste

Thüringer Werkstofftag 2021

6 LTCC layers (each layer created with 2 BCT6

Reaction and mixing chamber for microfluidics

Relatively good bonding between LTCC and Si

Silicon-ceramic composite substrates – from the laboratory to a robust process technology

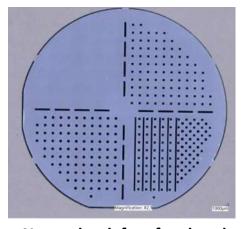

## 3. Fabrication of cavities – silicon side

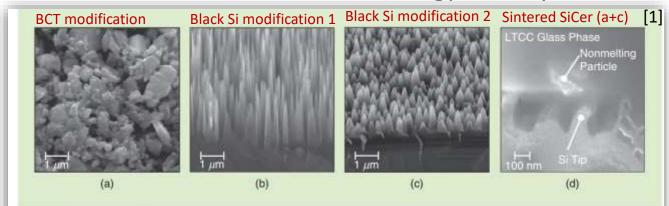

#### Silicon pre-processing:

- 1. 4 inch silicon wafer, unprocessed

- 2. Front: processing of contact pads, piezoresistive resistors, etc. Back: etching of membrane using KOH

- 3. applying black silicon at backside (optional)

- 4. sputtering of Ti layer at backside and oxidation to TiO<sub>2</sub>

#### Black Silicon:

- optimized RIE process

- criteria:

- no mountain formations

- homogeneity across the wafer

- specific needle height and width matched to the ceramic tape

Si surface after RIE processing

Silicon preprocessing [3]

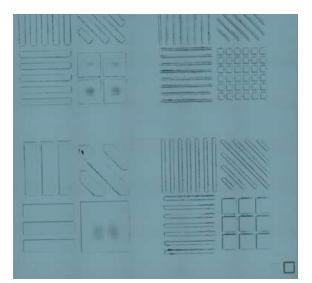

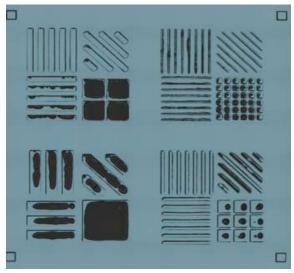

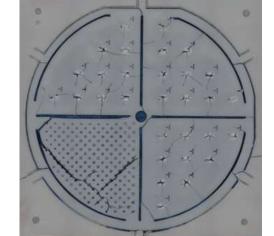

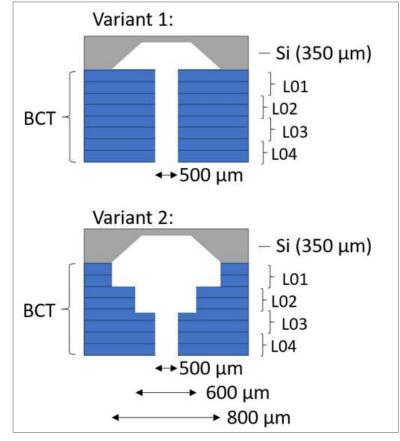

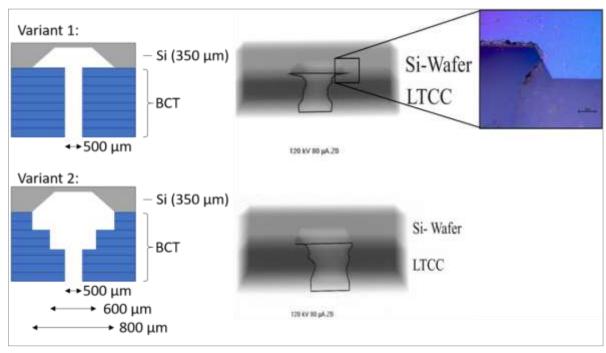

# 4. Layout and process optimization

- additional way to stabilise cavities by implementing sequential lamination

- standard: punched double tapes are stacked and laminated

- sequential: double tapes are individually laminated together

- production of two test layouts

- V1: 500 μm straight channel towards Si

- V2: widening channel, starting with 500 μm up to 800 μm

- seq. Lamination:

- (1) L03+L04 → L034

- (2) L02+L034 → L0234

- (3) W+L01  $\rightarrow$  WL01

- (4) WL01+L0234+Releasetape → WL01234R

Different ceramic channel construction [3]

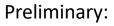

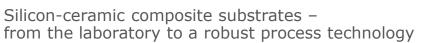

#### two-step cleaning process:

- preliminary cleaning

- fine cleaning

Water rinsing to remove loose releasetape particles

#### Fine cleaning:

- solvent cleaning in ultrasonic bath

- bake out

SiCer substrate with loose releasetape on both sides

Final SiCer substrate after cleaning process

VIA ELECTRONIC TECHNISCHE UNIVERSITÄT

ILMENAU

#### Chip-level examination:

- cross-sectional view

- burst pressure method

#### cross-sectional view:

- Microscopy

- **EDX**

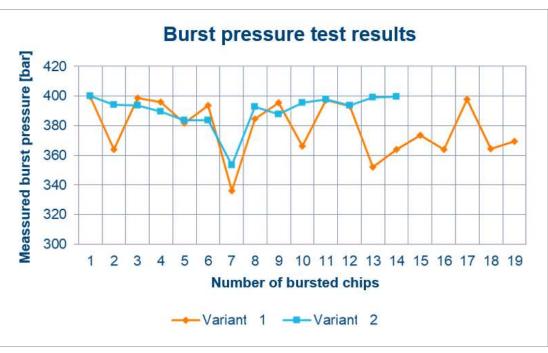

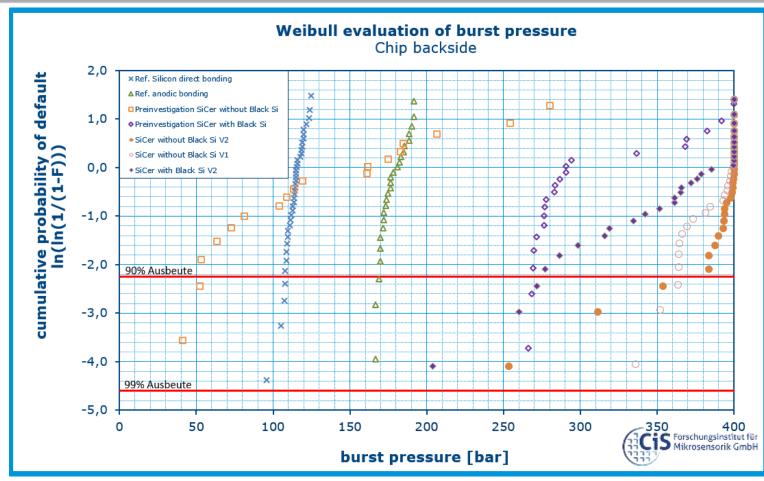

#### burst pressure method:

- destructive test method

- chip is glued onto special holder and tested up to max. pressure or bursting of sample

- measuring range limited to 400 bar

Cross-sectional view of both ceramic channel layouts after sintering process [3]

Thüringer Werkstofftag 2021

- total amount of 30 samples each tested

- typical fracture pattern or failures:

- fracture at bondinterface

- bulk material fracture

- detaching of adhesive bond

two exemplary fracture pattern (left: fracture at bondinterface, right: bulk material fracture) [3]

Comparison of both ceramic layout variants [3]

## 6. Conclusion and Outlook

- in total 7 measurement series, 5 with SiCer substrates

- clear improvement of burst pressure results with SiCer

- Best results achieved with

measurement series

- → widening channel and without black silicon at bondinterface

Burst pressure measuring results from different test samples [4]

ILMENAU

#### 6. Conclusion and Outlook

- Fluidic structures can be created at LTCC level with excellent shape by using carbon paste

- Bonding process has been evaluated and adapted to successfully bond Si and structured Ceramic wafers

- SiCer-substrates show increase of bonding strength at interface

- enlarging ceramic channel resolts in lower burst failure

- Black Silicon not necessarily needed for pressure sensors manufactured by pressure sintering process

#### **References:**

- [1] M. Fischer, et al.– Silicon-Ceramic Composite Substrate: A Promising RF Platform for Heterogeneous Integrations, IEEE Microwave Magazine 20, (DOI: 10.1109/MMM.2019.2928675), 28-34, 2019

- [2] Y. Fournier, 3D Structuration Techniques of LTCC for Microsystems Applications, PhD Dissertation, Swiss Federal Institute of Technology Lausanne (EPFL), 2010

- [3] C. Kleinholz, et al.: Implementation of SiCer technology for pressure sensor applications, CICMT Conference; 26.-29.04.2021

- [4] A. Cyriax, C. Kleinholz: Anwendungen von SiCer-Substraten bei Drucksensoren, HIPS Statusworkshop; 07.04.2021

Powered by SiCer - The best of both worlds

## Thank You For Your Attention!

VIA electronic GmbH

) + 49 36601 9298 114

m.bochard@via-electronic.de

www.via-electronic.de

Technische Universität Ilmenau

① + 49 3677 693385

cathleen.kleinholz@tu-ilmenau.de

www.tu-ilmenau.de/mne-et/